-

StatusOngoing

-

Status date2015-04-23

The PLIU is a unit containing command and acquisition channels of standard type, like High Level Commands and Thermistor acquisition channels. It contains power switches for heater control and stepper motor drivers. The interface to a central computer consists of a dual redundant Mil-Std-1553B bus.

The challenge is to make a low-cost production series by using commercial components and a production friendly design.

The main objective of this activity is to develop and qualify a Payload Interface Unit (PLIU) which will be used on the Iridium NEXT Satellites.

Another objective is that with the development of the Iridium NEXT PLIU, RUAG Space AB will be able to take a step against a more low-cost approach in future platform and payload computers/equipments by:

- Qualifying commercial EEE part for use in space,

- Developing I/O building blocks that can be used in future equipments.

The challenge is to make a low-cost production series by using commercial components and a production friendly design. It is clear that for Iridium NEXT PLIU Design to Cost solutions with high performances and integrated electronics components is encouraged and alternative EEE parts policy based on the experience of the suppliers are to be considered. For instance, commercial grade PED (Plastic Encapsulated semiconductor Device) has been investigated.

The development of the Payload Interface Unit (PLIU) for the Iridium NEXT constellation, consisting of 81 flight units have been very successful meeting performance and the low cost requirements.

This have been achieved with an early focus on produceability using a dedicated produceability working group, looking into the production aspect as well as part selection and design constraints.

The main cost driver from a design point of view in this program was identified as the cost for the parts. To cope with this, a price list was compiled for all potential parts that could be used within the design. The design was then adapted based on the cost for various parts. Several different design implementations were studied from a feasibility, risk and cost perspective. And a careful trade-off, with cost versus risk, was made with respect to the potential use of COTS-parts.

The PLIU is optimised for easy manufacturing considering the high production volume and rate. The electrical architecture and the mechanical design are based on two identical boards. The two boards operate in cold redundancy. Most cross-couplings are internal in the unit. The design is robust in all aspects with good margins for tolerances and variations. The level of integration is high to minimize cost and to maximize reliability.

Radiation hardness considering total dose and effects from heavy ions is achieved by careful design. This is achieved by thorough selection and testing of parts, combined with careful circuit design. Analyses is used to prove that worst case parameter drifts on parts level keep specified PLIU function and parameters within tolerances.

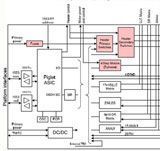

One PLIU unit consists of two identical boards with cross-coupled I/O signals and also heater and motor control signals routed via an internal motherboard. A block diagram of one board is shown in the figure below. The total I/O budget is thus in general two times the I/O channel numbers indicated to the right in the figure.

The PLIU provides the following platform interfaces:

- Power input

- TM/TC

- Dual redundant Mil-Bus-1553B

The PLIU provides the following user interfaces:

- 192 LLC Matrix pulse commands, internally cross-coupled,

- 96 DRM (relay switch matrix) acquisition channels, internally cross-coupled,

- 58 TH (thermistor interfaces) channels, internally cross-coupled,

- 30 ANAU (analogue acquisition) channels, internally crosscoupled,

- 24 heater outputs in total, divided into 12 failure independent groups, all accessible from both PLIU halves,

- 8 motor interface in total, each interface being failure independent, all accessible from both PLIU halves,

- Two ML16/DS16 buses per half, intended for external crosscoupling.

The development philosophy for the PLIU has been adapted to secure the design and development of the PLIU with the aim of getting a low-cost and highly suitable and producible module. The Iridium NEXT constellation requires 81 flight units, therefore a considerable effort has been made in the development phase to get a design suitable for smooth manufacturing and automated production tests.

To achieve this, several bread boards have been built before the EQM was manufactured:

- EBB

- IHBB1

- IHBB2

A success factor in meeting the performance requirements was the development approach with several bread boards during development phase where different design solutions have been tested. Moreover, the decision having two fit-checks for the antenna motor interfaces using first a bread board motor and secondly a flight representative motor, have further decreased the risk of having a non-optimum design solution.

The use of SMD parts have been maximized, an SMD 1553 transformer has been introduced, all external connectors are designed to be directly soldered on the PCB, all chassis mounted components is soldered directly to the PCB. Only one type of ferrite core is used for the integrated magnetics, i.e. planar transformers.

The PLIU EQM test campaign has been successfully performed.