-

StatusOngoing

-

Status date2022-10-11

-

Activity Code7B.058

The aim of the project is the implementation of a fully software defined DVB-S2X demodulator, running on general-purpose hardware, which could replace a dedicated hardware demodulator in some selected use cases. The technical challenges of parallel processing for demodulation and decoding algorithms in software will be elaborated. Based on existing implementations and partially new designs, the dedicated exploitation of hardware-specific elements is expected to achieve bandwidths of 36 MHz and beyond, matching the application-specific requirements.

There are two main technical challenges connected to the design of a real-time software demodulator:

-

In the first place, several algorithms traditionally oriented to hardware implementations have to be adapted to a software paradigm. This is particularly challenging due to the variable frame size used in the DVB-S2X physical layer.

-

On a more implementation-oriented basis, the features offered by the hardware platform (e.g., SIMD instruction set extensions) shall be intensively exploited.

DVB-S2X due do its performance potential has become a widely used waveform in satellite communications across multiple application scenarios. With digitisation advancing and virtual cloud-based processing on the rise, moving DVB-S2X reception to generic processing platforms is a logical step forward. This step creates completely new possibilities in this area.

-

Runs on generic purpose processors

-

Demodulation and channel decoding compliant to ETSI EN 302 307 (QPSK, 8-PSK, 16-APSK at minimum)

-

Full processing chain from digitized IQ samples to decoded BBFRAMEs over IP

-

Supports IEEE-ISTO Std 4900-2021 for input samples

-

Supports CCM, VCM and ACM

-

Supports time slicing (Annex-M ETSI EN 302 307-1)

-

Designed for local and cloud deployment

-

Modular design for future extension to different waveforms

-

Throughput of 36 Mbps and beyond (on x86 CPUs with AVX2 support)

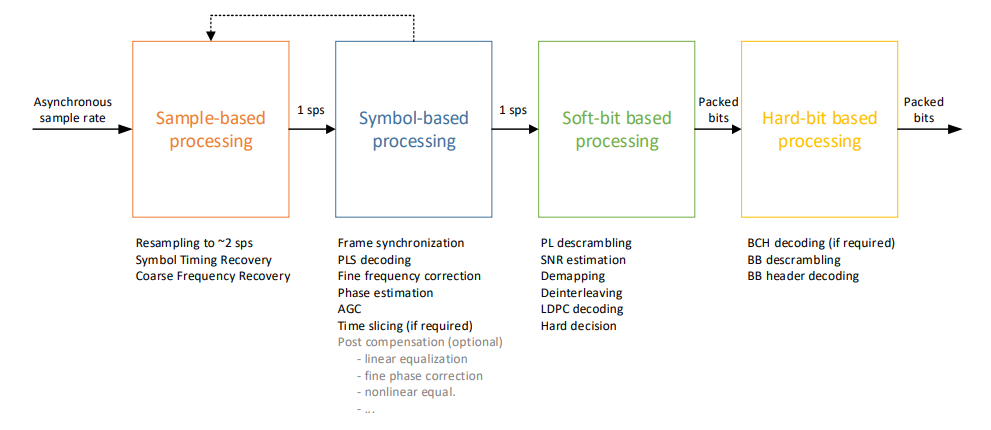

The architecture of the SWDM is implicitly dictated by the data types and rates which shall be processed at each step. The DVB-S2 implementation guidelines provide a reference demodulator architecture and a detailed explanation of several algorithms. Nevertheless, the latter are thought for a conventional hardware realization of the receiver and cannot always be directly mapped to a software architecture. It is understood that some of the macro-blocks are particularly challenging for a software implementation. A possible breakdown of the receiver into macro-blocks is shown in the Figure.

The project follows a familiar waterfall project process:

-

System Requirements Review, Q1 2022: Definition of applications and requirements, State-of-the-Art analysis, Creation of technical specification & Outline verification plan

-

Preliminary Design Review, Q3 2022: Select a Technical baseline selection & establish a Preliminary Design

-

Critical Design Review, Q4 2022: Establish a Detailed Design, Integration Plan and Test Plan

-

Test Readiness Review, Q1 2023: Implementation of the deliverable Items and first test runs.

-

Final Presentation, Q3 2023: Final Review and perform critical assessment of potential of developed items for commercial exploitation

The activity was kicked off in January 2022 and has achieved the System Requirements Review (SRR).

Work currently in progress.