-

StatusOngoing

-

Status date2020-09-25

-

Activity Code6B.055

The objective of this project is to develop and test a prototype of an analog IF over digital IF acquisition/generation demonstrator for instantaneous signal bandwidth up to 5GHz, together with a set of data compression techniques with the scope to minimize the digital IF data rate required to transmit a given analog IF bandwidth, optimized for each of the operational scenarios identified.

The key challenges of the project are:

- Hardware implementation to support the very high bandwidth

- Design and implementation of efficient compression algorithms that can support the high bandwidth

- Sensitivity of the “conventional” signal processing (once the signal is reconstructed) to the compression/decompression (FER sensitivity)

- Choice of adapted network protocols and technologies to enable real-time transport of digitized RF signal

The RF over IP demonstrator developed in this project supports significantly higher simultaneous bandwidths than any other RF over IP product commercially available in 2020.

Product features:

- Support for very wide bandwidths up to 5 GHz

- Support for duplex communications

- Optimized compression for wide frequency bands with multiple TDM carriers (e.g. DVB-S2X) and multiple MF-TDMA carriers (e.g. DVB-RCS2)

- Use of a combination of lossless and lossy compression techniques

- Digital interface compliant with open standards, such as VITA 49/eCPRI

- Built-in Ka-band interface (24-44 GHz)

- Support for satellite communication using both GEO and non-GEO orbits

The main use case scenario is for use with VSAT systems where the wideband RF over IP module is placed at the antenna sites and typically communicated with digital modems with RF over IP interfaces via a high-speed fiber connection as shown in the figure below.

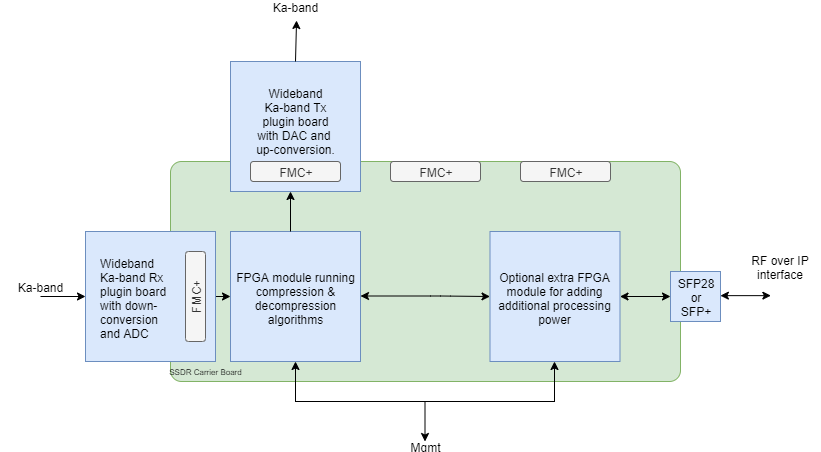

The block diagram below illustrates a candidate hardware platform for implementing the demonstrator where the following modules are plugged into a carrier board:

- 2 high-capacity, powerful FPGA SoC modules configured with large Xilinx UltraScale+ SoC FPGAs that are running the compression algorithms.

- Wideband RF front-end modules supporting frequency conversion from RF to baseband / baseband to RF and optionally also the analogue-to-digital and digital-to-analogue conversion for the 5 GHz bandwidth.

The duration of the project is 29 months, with the following milestones:

- Kick-off: May 2020

- System Requirement Review (SRR): September 2020

- Critical Design Review (CDR): June 2021

- Factory Acceptance Review (FAT): June 2022

- On-site Acceptance Review (SAT): August 2022

- Final Review (FR): September 2022.

The project kick-off was on May 13, 2020 and the System Requirement Review (SRR) was held on September 3, 2020. Ongoing work is identification of state-of-the-art techniques for compression, evaluation of the theoretical gain we can get from compression, identification of compression techniques to be used and evaluation of compressed sensing. The next milestone is the Critical Design Review (CDR).