-

StatusCompleted

-

Status date2022-04-13

-

Activity Code4G.031

The main objectives of the project are:

-

Assemble the GR740 die in a suitable plastic package.

-

Complete a verification of the product performance via a suitable test program demonstrating the capability to reach required standards for SATCOM constellation programs (i.e. reach TRL 7).

-

Confirm that the Product is ready for entering in a validation stage with operational users.

-

Ensure that the design implementing the full set of requirements are possible to implement in a suitable package.

-

Ensure there are no problems related to new supplier relationships that potentially could result in quality or lead-time issues.

-

Reduce probabilities that complex designs with e.g. crossed wires are not needed.

-

Ensure resources are available.

-

Ensure there are no problems related to transfer of Test Program for new supplier and component variant compared to the ceramic.

-

Ensure there is no package warpage.

-

Ensure there is no delamination at sawing due to low K dielectrics.

-

Existing die from a ceramic variant manufactured for QML flow can be used.

-

Wafer and assembly lot traceability is supported to a higher extent compared to what is normally maintained for COTS parts.

-

High electrical performance.

-

Defined radiation characteristics.

-

Existing software support.

-

No US content.

The specific features related to the new PBGA package:

-

Plastic Ball Grid Array (PBGA); 625 balls

-

Body Size: 27x27mm

-

Balls matrix: 25x25mm

-

Package thickness: 2.39mm

-

Substrate: 4L

-

Solder Ball pitch: 1mm

-

Solder Ball diameter: 0.6mm

Specifications for the entire product:

-

System frequency: 250 MHz

-

Main memory interface: PC100 SDRAM

-

SpaceWire router with SpaceWire links 200 Mbit/s minimum

-

33 MHz PCI 2.3 initiator/target interface

-

Ethernet 10/100/1000 Mbit MACs

-

PBGA625 package

-

Quality ECSS-Q-ST-60-13C, class 2

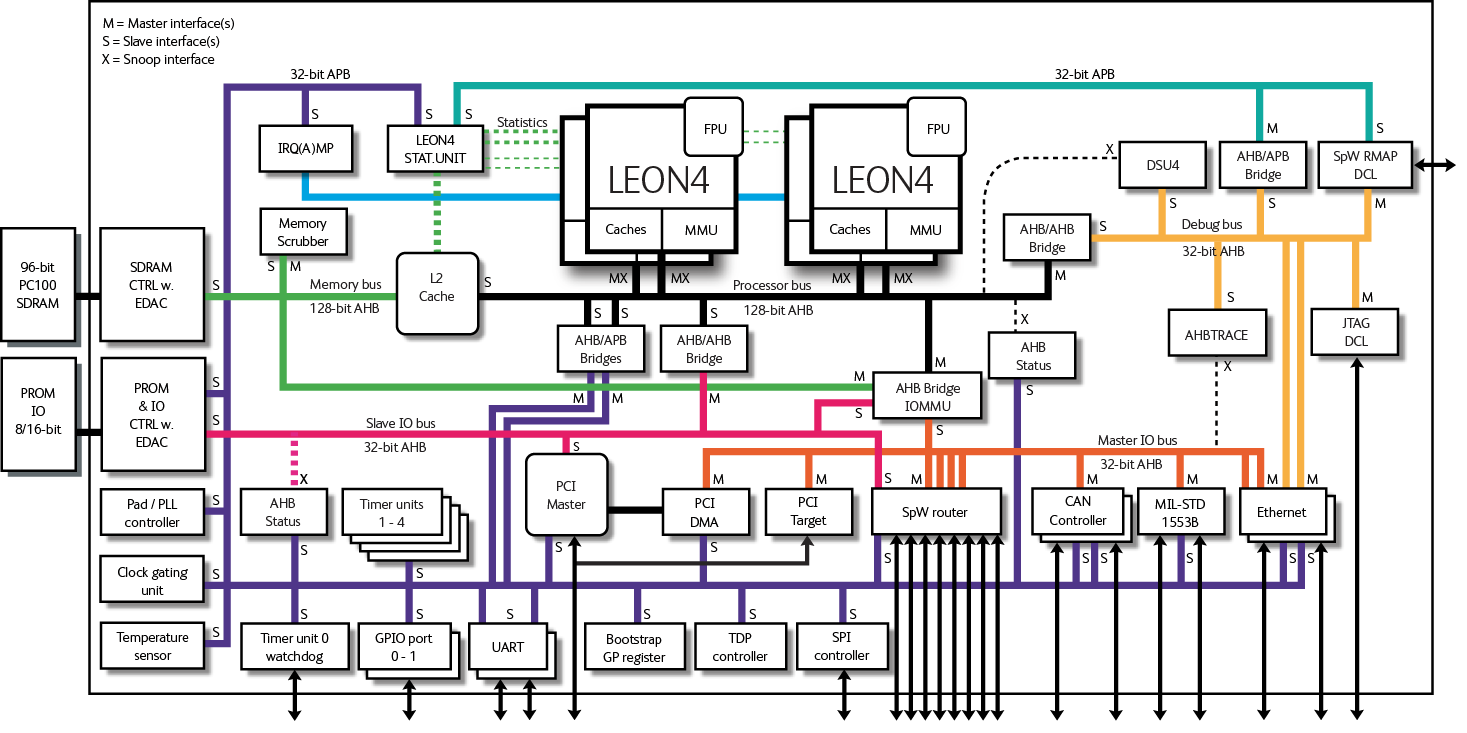

The figure below illustrates the architecture for the entire product.

-

Fault-tolerant quad-processor SPARC V8 integer unit with 7-stage pipeline, 8 register windows, 4x4 KiB instruction and 4x4 KiB data caches.

-

Double-precision IEEE-754 floating point units

-

2 MiB Level-2 cache

-

64-bit PC100 SDRAM memory interface with Reed-Solomon EDAC

-

8/16-bit PROM/IO interface with EDAC

-

SpaceWire router with eight SpaceWire links

-

2x 10/100/1000 Mbit Ethernet interfaces

-

PCI Initiator/Target interface

-

MIL-STD-1553B interface

-

2x CAN 2.0 controller interface

-

2x UART, SPI, Timers and watchdog, 16+22 pin GPIO

-

CPU and I/O memory management units

-

Multi-processor interrupt controller with support for asymmetric and symmetric multiprocessing

-

SpaceWire TDP controller and support for time synchronization

-

JTAG, Ethernet and SpaceWire debug links

From an architectural point of view, the new plastic package variant does not differ from the ceramic variant.

The project consists of the following major work packages and milestones:

WP210 Preparations and planning

WP220 Substrate design and tooling

WP230 Test solution, part 1

WP240 Preparation burn-in tests

Milestone 1 – Critical Design Review

WP230 Test solution, part 2

WP310 Prototype and EQM manufacturing

WP320 Evaluation

Milestone 2 – Test Review Board

WP330 Industrialization

WP100 Project management

Milestone 3 – Final Review

Activity completed. An updated Data Sheet that includes the PBGA variant has been published.