-

StatusCompleted

-

Status date2019-07-09

-

Activity Code5C.104

The aim of ARTES 5.1 2012 research activities was to evaluate the EPC components, technologies and processes limiting the operation at high base plate temperature 100°C of the overall SSPA – EPC architecture. This means that substrate temperature could reach about 115°C and components, materials and technologies must therefore be improved to withstand continuous operation with such high thermal constraints.

The challenge is to have a single product developed, with different options depending on input/output characteristics using the same technologies, the same electrical architecture, the same electronic design modules, a common definition and justification file, the same PCB, and a maximum of common EEE parts.

The expected benefits are to answer the expectations of innovative equipment to be used in the near future for telecommunication applications with a market target cost product.

The features of the product are:

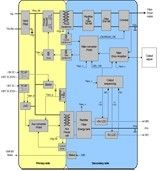

In the following figure the main blocks for the baseline architecture are represented:

The development plan has been based on 3 phases:

- Phase 1. Preliminary specification and architectural SSPA design. This phase included the investigation on components and technologies enabling high temperature operation.

- Phase 2. Converter design including the identification of critical blocks.

- Phase 3. Manufacturing and test of HW to be able to characterize the design in thermal vacuum conditions. An analysis of the results has been used to perform and propose design improvements for the high temperature converter. Results have shown that the efficiency could be easily improved by using GaNFets.

The project has been completed with very good results.

Significant goals have already been reached with the selected components and packaging, especially if a second 125°C step is to be considered. Yet, further analysis and tests need to be performed to validate and qualify long term operating life in GEO.

The current EPC design, under this Artes 5.1 activity, has shown good performances at 100°C operation upon technological aspects and electrical ones, thus fulfilling successfully the objective of this study. Morever, the use of GaNfets has opened many possibilities in terms of efficiency increase, higher switching transitions and frequencies, and EPC volume reduction.

Finally, the availability of a high temperature SSPA based on GaN for the RF-tray, and on GaN for the DCDC converter, can be expected by 2015.