-

StatusCompleted

-

Status date2010-12-06

-

Activity Code5A.007

The project is aimed at defining the architecture of a fully reconfigurable regenerative onboard processor (OBP), based on a reconfigurable technology available for space applications today or in a short term.

A safe communication protocol is also to be defined to transfer the reconfiguration data on the uplink RF channel. The OBP architecture, and the communication protocol, are implemented and tested using commercial off-the-shelf equipments based on the selected technology components (XILINX Virtex-4 FPGA family, already available in space-qualified version).

The project has several objectives:

- The definition of a reference scenario, in terms of applications and functional requirements, for a next generation reconfigurable onboard processor;

- A comparative analysis of the technologies suitable for the implementation of a fully reconfigurable, regenerative processor and the selection of a candidate technology based on its capabilities and its availability for space-based applications;

- The definition of the functions and the architecture of a reconfigurable onboard processor based on the selected reconfigurable technology;

- The definition of a reconfiguration methodology, capable to provide a reliable, efficient and secure reconfiguration of the onboard processor;

- The definition of the architecture of a processor prototype, based on the selected reconfigurable technology, and its implementation, using commercial off-the-shelf equipments, to verify the capabilities of the defined architecture in terms of achievable reconfiguration levels and ease of reconfiguration;

- The definition of the functions and the architecture and the manufacturing of a validation environment, to test the processor prototype.

The main focus of the project is to verify the level of flexibility offered by an OBP architecture based on a fully reconfigurable technology and to test the effectiveness of the reconfiguration protocol.

Another relevant issue is to check the OBP continuity of service during a partial reconfiguration, a feature offered by the particular implementation technology selected.

The OBP validation tests will also allow to measure the time required to apply the different kinds of reconfigurations, from the time needed to transmit the data on the RF channel to that required to transfer the data in the FPGAs configuration memory.

The regenerative OBP platform under development is based on the high performance Xilinx Virtex-4 FPGAs already available for space applications. Though SRAM-based reconfigurable devices were already used in space both in ESA and NASA projects, the main drivers there have been development time and cost; now the focus is on the exploitation of the full reconfiguration capabilities to add a level of flexibility never reached so far for a reconfigurable OBP.

The main benefit of a fully reconfigurable architecture is its adaptability in-flight to cope with new requirements or with new/changed market scenarios; this capability is extremely valuable for a device relying on an access protocol to use the communication resources, as the possibility to adapt the air interface removes what is probably perceived as the heaviest constraint of a regenerative OBP.

An FPGA-based architecture also has an advantage, w.r.t. a classical ASIC-based architecture, in terms of development time and cost savings, especially for complex equipments as the OBPs which are not produced in high quantities (when an ASIC is still cheaper).

On the other hand, it has to be considered that the FPGAs are rad-tolerant devices, then single error mitigation techniques must be adopted, reducing the performance (processing speed and available resources) and increasing the design complexity; these disadvantages may be overcome basing the OBP architecture on the recently qualified Virtex-5, rad-hard devices.

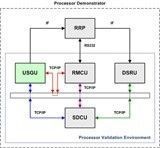

The architecture of the Reconfigurable Regenerative Processor (RRP) prototype is the classical architecture of a regenerative OBP, as shown in the diagram below.

The fully reconfigurable portion of the OBP is the U/L Channel Processor (UCP), which provides the processing of the input signal: the Input Channel Demultiplexer, the Multicarrier Demodulator and the Decoder & Output Stream Formatter.

The input signal is a DVB-RCS compatible, multicarrier input channel carrying five different carrier types, with data rates ranging from 0.5Mbps to 8Mbps; the output signal is a DVB-S2 compatible channel.

The UCP architecture allows five different kinds of reconfiguration:

- A Full Reconfiguration, which consists of the complete reconfiguration of the onboard processor, loading a new set of configuration data;

- A Partial Reconfiguration with new algorithms, consisting of the modification of only a portion of the configuration data defining the behaviour of the processor;

- An Algorithms Upgrade, a limited reconfiguration affecting the configuration data relevant to one or more signal processing algorithms;

- A Parameters Update, a very limited reconfiguration affecting the parameters which control the behaviour of the signal processing algorithms;

- A Functions Add-on, consisting of adding one or more new functions/algorithms to upgrade the functionalities of the onboard processor or to satisfy new requirements.

The UCP is implemented using an HAPS-32 board from Synplicity, housing two Xilinx Virtex-4 LX160 FPGAs; daughter boards are also included to provide ancillary functions (A/D conversion, data storage, I/O interface, etc…). The UCP includes an FPGA-based control section which handles the reconfiguration protocol and actually reconfigures the HAPS-32 FPGAs through the JTAG interface.

The RRP prototype is surrounded by four units which generate the input channel (USGU), acquire the output channel to evaluate different statistics (DSRU), control the OBP (RMCU) and coordinate all the OBP reconfiguration and verification operations (SDCU).

The contractual kick-off was on July 1st, 2007.

Two phases are planned:

Phase 1, to devise a reference system scenario, make a survey of the reconfigurable technologies and select a technology to implement the OBP prototype, consolidate the architecture of the OBP and of the units of the OBP demonstration environment;

Phase 2, to carry on the detailed design and the manufacturing of the OBP and the ancillary units and to perform the validation tests.

The Phase 2 of the project was successfully closed on October, 2010.

The test campaign proved the capability of the proposed architecture to implement a fully reconfigurable regenerative: following a well defined reconfiguration procedure, it was possible to perform all the required reconfiguration categories, from the simple update of parameters to the full reconfiguration.

The reconfiguration procedure is easily implemented using the communication channel: no dedicated carriers are needed and the reconfiguration data are transported using the traffic bursts.

The reconfiguration procedure does not affect the nominal operations of the OBP during the upload of the reconfiguration data; the nominal operations are interrupted only when the reconfiguration data are transferred to the FPGA configuration memory, for a time that is around 90s for the full reconfiguration of a Virtex-4 LX160 FPGA using the JTAG interface.

In the end, the high level of flexibility obtained with the proposed architecture may constitute a new opportunity for the regenerative onboard processors, allowing exploiting the added value provided by the regeneration of the signal without the drawback of the dependence from an air interface that cannot be modified after the satellite deployment.

The project is completed.