-

StatusOngoing

-

Status date2023-06-28

-

Activity Code7-.047

The objective of this project is to develop and verify a high-end Digital Modem SDR Platform with 100 Gbps RF over IP interface. While the Digital Modem is a generic SDR platform, the application demonstrated on the platform in this project is a high-speed DVB-S2X modem supporting baud rates up to 1.4 Gbaud and user data rates up to 7 Gbit/s.

The key challenges of the project are:

-

High RF bandwidth requires large bandwidth on the digital fibre link (e.g. 1.25 x oversampling of a 1.5 GHz signal bandwidth requires 37.5 Gbit/s when transmitting 10 bits complex data)

-

User data rates of up to 7 Gbit/s (DVB-S2X with 32 APSK x 1.4 Gbaud) require high processing bandwidth.

-

SW framework for COTS FPGA acceleration modules

-

Support for antenna diversity

-

Make redundancy switching easier and replace IF switch matrix(es)

-

Move modem processing to software defined radio architecture

-

Option to do the modem processing on different location(s) than at the antenna location

-

Use COTS hardware for modem processing

Product Features:

-

DVB-S2X Modem (transmitter + receiver)

-

User data up to 7 Gbit/s

-

Baud rates up to 1.4 Gbaud

-

RF bandwidth up to 1.5 GHz

-

-

VITA49.2 RF-over-IP interface over 100 Gbit/s Ethernet

The block diagram below shows an example VSAT system using RF-over-IP on the Teleport.

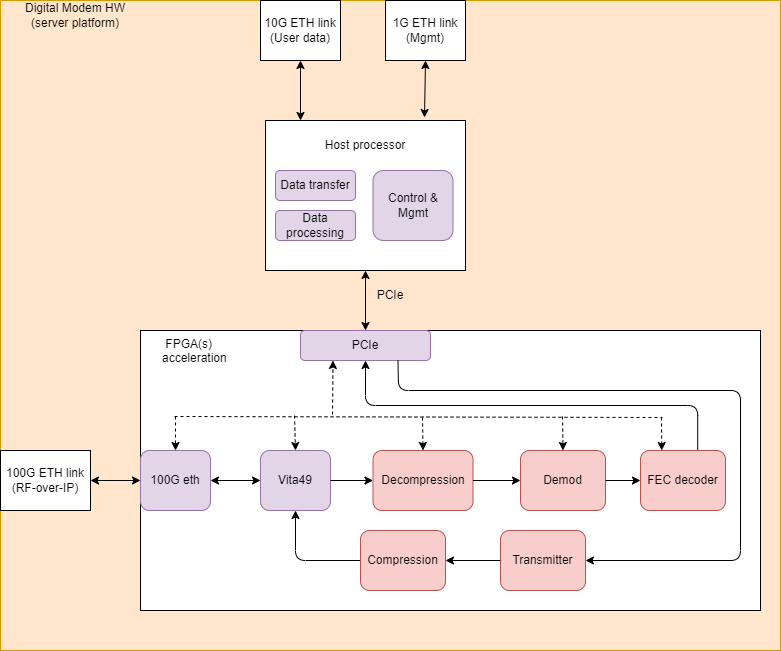

The key components in the digital modem are the DVB-S2X demodulator and FEC decoder and DVB-S2X transmitter, in addition to the VITA49.2 and 100G ethernet interface as indicated in the block diagram below. Optionally, the digital modem may support compression and decompression logic to minimize the data rate between the RF-over-IP device and the digital modem. The DVB-S2X components are re-used from previous ARTES activities.

The HW platform is a COTS server equipped with a COTS FPGA acceleration module.

The duration of the project is 10 months with the following milestones:

-

Kick off meeting (KO): November 2022

-

Mid-Term Review (MTR): May 2023

-

Final Review (FR): September 2023

The project was kicked off on November 29’th 2022. COTS components have been selected and acquired and ongoing work is to specify the detailed requirements as well as getting a new design-flow up running. The next milestone is Mid-Term Review (MTR) in May 2023.